微眾信科IPO成功過會,云鑫創投為第二大股東,探索互聯網信息服務新藍圖

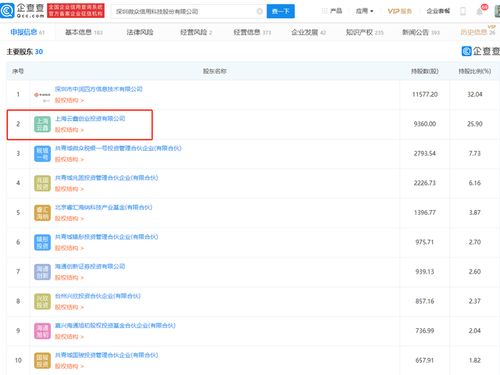

深圳微眾信用科技股份有限公司(以下簡稱“微眾信科”)首次公開發行股票并在科創板上市的申請成功通過上海證券交易所上市委員會審核,標志著這家專注于信用科技服務的公司即將登陸資本市場。這一消息在金融科技領域引起了廣泛關注,不僅因為微眾信科自身的業務前景,更因其股東背景中出現了螞蟻集團旗下云鑫創業投資有限公司的身影,云鑫創投作為第二大股東,持股比例顯著,進一步凸顯了互聯網巨頭在信用科技與信息服務領域的戰略布局。

微眾信科作為一家以大數據、人工智能和區塊鏈等前沿技術驅動的信用科技服務商,其核心業務是為金融機構、企業及政府提供包括信用風險評估、信用解決方案、數據風控模型在內的多元化互聯網信息服務。公司依托深厚的技術積累和豐富的場景應用經驗,致力于破解傳統信貸中的信息不對稱難題,提升金融服務的可得性與效率。在數字經濟高速發展的當下,微眾信科的成功過會,無疑為信用科技行業注入了新的活力,也預示著互聯網信息服務在金融領域的深化應用將迎來更廣闊的空間。

值得注意的是,螞蟻集團通過云鑫創投持有微眾信科重要股份,這一股權關聯不僅為微眾信科帶來了資本支持,更可能促進雙方在技術、數據和生態層面的協同。螞蟻集團作為全球領先的金融科技平臺,其在信用評估、風險控制及普惠金融方面的成熟經驗,有望與微眾信科的專項服務形成互補,共同推動信用科技基礎設施的完善。這種合作模式也反映了當前互聯網信息服務行業的一個趨勢:頭部企業通過投資布局,整合產業鏈資源,以構建更強大的數字生態體系。

從行業角度看,微眾信科的IPO過會具有多重意義。它體現了監管層對信用科技及互聯網信息服務創新的認可與支持,為同類企業提供了上市路徑參考。隨著數據安全與隱私保護法規的日益嚴格,微眾信科如何平衡技術創新與合規經營,將成為市場關注的焦點。公司需在信息服務中確保數據使用的合法性與安全性,這對其長期發展至關重要。微眾信科的成功也有望吸引更多資本涌入信用科技賽道,加速行業整體技術升級和服務優化。

微眾信科登陸科創板后,將獲得更多融資渠道,有助于加大研發投入,拓展服務場景,尤其是在小微企業信貸、供應鏈金融等薄弱領域發揮更大作用。而云鑫創投作為戰略股東,或將在資源對接、市場拓展方面提供助力,共同探索互聯網信息服務的新模式。在數字化浪潮中,信用科技正成為連接金融與實體經濟的關鍵紐帶,微眾信科的上市進程或將成為這一領域發展的里程碑事件,推動整個行業向更高效、更智能的方向邁進。

微眾信科IPO過會不僅是企業自身的成長飛躍,也是互聯網信息服務與金融科技融合發展的生動縮影。在螞蟻集團等巨頭的加持下,微眾信科有望在資本市場中嶄露頭角,為構建可信、普惠的數字經濟生態貢獻更多力量。隨著上市鐘聲的臨近,市場期待看到其在合規框架下,如何以創新服務賦能社會信用體系建設,書寫互聯網信息服務的新篇章。

如若轉載,請注明出處:http://www.uaiin.cn/product/51.html

更新時間:2026-05-06 16:00:22