谷歌調整產品搜索服務,商業模式變革引商家關注

谷歌宣布對其產品搜索服務進行重要調整,計劃開始向商家收取費用,這一舉措引發了互聯網信息服務領域的廣泛關注。作為全球領先的搜索引擎,谷歌的這一變革不僅反映了其商業策略的調整,也可能對電商生態和商家運營模式產生深遠影響。

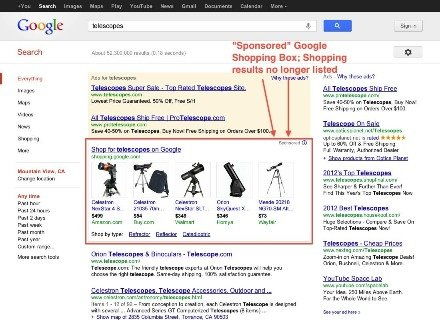

長久以來,谷歌的產品搜索服務(現為“谷歌購物”)為消費者提供了便捷的商品比價和購買渠道,而商家則通過免費或低成本的方式展示產品信息,從而獲得流量和潛在客戶。隨著市場競爭加劇和數字化轉型的深入,谷歌此次收費政策的推出,標志著其從傳統廣告模式向更直接商業服務轉型。

具體來說,谷歌將要求商家支付一定費用,以便在搜索結果中更突出地展示產品信息,例如圖片、價格和評價等。這一變化旨在提升搜索結果的商業價值,同時為谷歌帶來新的收入來源。對于商家而言,這意味著需要重新評估在線營銷預算,權衡付費展示與自然流量之間的平衡。大型電商企業可能更容易適應這一變革,而中小商家則可能面臨成本壓力和競爭挑戰。

從行業角度看,谷歌的調整反映了互聯網信息服務向更精細化、商業化方向發展的趨勢。隨著用戶數據隱私法規的加強和廣告攔截技術的普及,搜索引擎公司正尋求多元化收入模式,以降低對傳統廣告的依賴。此舉也可能推動其他平臺(如亞馬遜、社交媒體)跟進類似收費策略,進一步重塑電商競爭格局。

商家應如何應對這一變化?專家建議,優化產品信息和網站用戶體驗,以提升自然搜索排名;合理分配營銷預算,結合付費搜索和內容營銷等策略;關注新興渠道(如短視頻、直播電商),以分散對單一平臺的依賴。消費者方面,短期內可能看到更精準的產品推薦,但長期需注意商業化可能帶來的信息偏見。

谷歌的這次調整是互聯網信息服務演進中的一個重要節點,它提醒我們:在數字化時代,商業模式的創新與平衡至關重要。商家、平臺和消費者之間的互動將更加復雜,唯有適應變化,才能在競爭中脫穎而出。

如若轉載,請注明出處:http://www.uaiin.cn/product/54.html

更新時間:2026-05-06 22:28:14