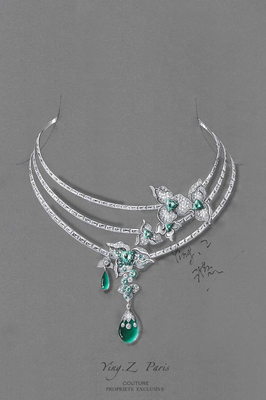

互聯(lián)網(wǎng)時代珠寶選購指南 告別陷阱,盡享璀璨

在互聯(lián)網(wǎng)信息服務(wù)的推動下,珠寶消費已不再是遙不可及的奢侈體驗。通過在線平臺,消費者可以輕松瀏覽琳瑯滿目的珠寶款式,從經(jīng)典鉆石到獨特設(shè)計,每一件都閃耀著誘人的光彩。更重要的是,借助用戶評價、專業(yè)認(rèn)證和透明的價格比較,消費者能夠有效規(guī)避傳統(tǒng)市場中常見的‘坑’,如虛標(biāo)材質(zhì)、夸大宣傳等問題。現(xiàn)在,只需輕點鼠標(biāo),就能放心挑選心儀的珠寶,讓每一次購物都成為美的享受。

如若轉(zhuǎn)載,請注明出處:http://www.uaiin.cn/product/29.html

更新時間:2026-05-06 17:18:15