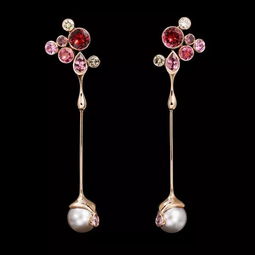

LV御用珠寶設計師 用智慧點亮璀璨珠寶藝術

他曾是路易威登(Louis Vuitton)的御用珠寶設計師,在珠寶設計領域享有盛譽。憑借舉世無雙的智慧與創造力,他將珠寶與藝術融合,打造出一系列美輪美奐的珠寶首飾,每一件作品都閃耀著獨特的靈魂與精湛的工藝。

在他的設計生涯中,他不僅注重珠寶的審美價值,還融入了深厚的文化內涵和創新理念。他的作品常常以細膩的線條、獨特的材質和富有象征意義的元素著稱,贏得了全球時尚界和收藏家的高度贊譽。從項鏈、戒指到耳飾,每一件珠寶都仿佛在訴說著一個故事,展現著設計者的思想與情感。

隨著互聯網信息服務的普及,他的作品和設計理念得以更廣泛地傳播。通過線上展覽、社交媒體分享和數字平臺展示,更多人有機會欣賞到他的杰作,學習他的設計哲學。這不僅推動了珠寶藝術的全球化發展,也激勵了新一代設計師勇于創新。

總而言之,這位設計師用智慧與才華將珠寶藝術推向新高度,讓互聯網信息服務成為連接藝術與世界的橋梁。

如若轉載,請注明出處:http://www.uaiin.cn/product/27.html

更新時間:2026-05-06 17:32:19